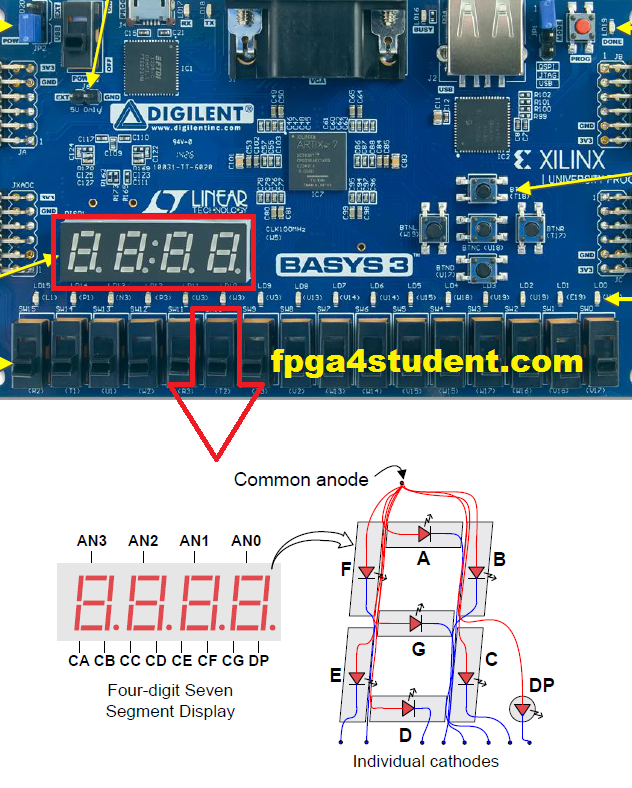

Last time, I presented an FPGA tutorial on how to control the 4-digit 7-segment display on the Basys 3 FPGA board. Full Verilog and VHDL code for displaying a 4-digit number on the 7-segment display of FPGA Basys 3 were also provided.

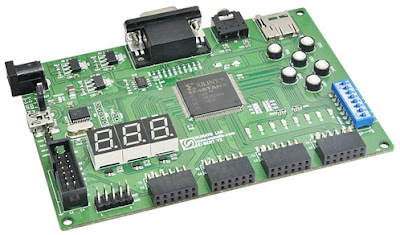

This FPGA tutorial tells you how to interface a mouse with Xilinx Basys 3 FPGA board. The FPGA tutorial also provides a Verilog code for interfacing a mouse with FPGA Basys 3.