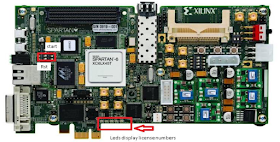

A plate license recognition system is implemented in Matlab and then it is implemented on FPGA Xilinx Spartan-6 using Verilog. Below is the test environment for the system on FPGA.

Image memory: 10 images and convert it into .dat format ( gray data). We use $readmemh(synthesizable) Verilog command to initialize the memory by reading gray data from .dat file. 10 images are converted into Gray format and write to the .dat file by using Matlab.

Plate License Recognition core: Use a switch on FPGA as the “start” signal to trigger this core working and output the plate license numbers.

Monitor on LEDs: When the “done” signal is rising-edge, this block periodically displays plate license numbers.

Top level Verilog code for testing the license plate recognition system:

// fpga4student.com FPGA projects, Verilog projects, VHDL projects // Verilog project: License Plate Recognition in Verilog and Matlab // Top level module for testing the license plate recognition system module Test_top(input clk // 33MHz ,rst, start, output reg[5:0] led ); reg [7:0] image_pixel_val; // Outputs wire done; // fpga4student.com FPGA projects, Verilog projects, VHDL projects wire [15:0] image_pixel_addr; wire [5:0] ReadCh; reg[5:0] num1,num2,num3,num4,num5,num6,num7; reg [2:0] count,count_4s; wire CharCheck; reg clk_4s,display; integer counter; reg [7:0] image_inv [0:65535]; // Instanitate the license plate recognition system LPChRec uut ( .clk(clk), .rst(rst), .start(start), .image_pixel_val(image_pixel_val), .image_pixel_addr(image_pixel_addr), .ReadCh(ReadCh), .CharCheck(CharCheck), .done(done) ); // Read License Plate Image file into FPGA initial begin $readmemh ("10.dat", image_inv, 0, 65535); end always @(posedge clk or posedge rst) // clock 4s begin if(rst) begin clk_4s <= 1'b0; counter <= 0; end else begin counter <= counter + 1; if(counter <= 66000000) clk_4s <= 1'b0; else if(counter > 132000000) begin counter <=0; end else clk_4s <= 1'b1; end end always @(posedge clk) begin image_pixel_val <= image_inv[image_pixel_addr]; end // fpga4student.com FPGA projects, Verilog projects, VHDL projects always @(posedge clk or posedge rst) begin if(rst) begin count = 3'd0; num1 <= 40; num2 <=0; num3 <= 0; num4 <= 0; num5 <= 0; num6 <= 0; display <= 0; end else begin if(CharCheck) begin count = count + 1'd1; if(count==3'd1) num1 <= ReadCh; else if(count==3'd2) num2 <= ReadCh; else if(count==3'd3) num3 <= ReadCh; else if(count==3'd4) num4 <= ReadCh; else if(count==3'd5) num5 <= ReadCh; else if(count==3'd6) num6 <= ReadCh; else if(count==3'd7) num7 <= ReadCh; else begin num1 <= 0; num2 <=0; num3 <= 0; num4 <= 0; num5 <= 0; num6 <= 0; end end if(done) display <= 1; end end // fpga4student.com FPGA projects, Verilog projects, VHDL projects always @(posedge clk_4s or posedge rst) begin if(rst) begin count_4s <= 0; led <=0; end else begin if(display) begin count_4s <= count_4s + 1; if(count_4s==0) led <= num1; else if(count_4s==1) led <=num2; else if(count_4s==2) led <=num3; else if(count_4s==3) led <=num4; else if(count_4s==4) led <=num5; else if(count_4s==5) led <=num6; else if(count_4s==6) led <=num7; else count_4s <= 0; end end end endmodule

Verilog code for License Plate Recognition System:

// fpga4student.com FPGA projects, Verilog projects, VHDL projects // Verilog project: License Plate Recognition in Verilog // Top level Verilog code for License Plate Recognition module LPChRec( input clk, input rst, input start, input [7:0] image_pixel_val, output [15:0] image_pixel_addr, output [5:0] ReadCh, output CharCheck, output done ); wire [7:0] ccl_th_low; wire [7:0] ccl_th_high; wire [7:0] image_pixel_val1; wire [15:0] image_pixel_addr1; wire [15:0] ImgAddr; wire [7:0] ImgVal; wire [7:0] ObjAddr1; wire [55:0] ObjInfo; wire ccl_done,active; assign ccl_th_low = 8'd40; assign ccl_th_high = 8'd255; assign image_pixel_addr = (active)?ImgAddr:image_pixel_addr1; assign image_pixel_val1 = image_pixel_val; assign ImgVal = image_pixel_val; // fpga4student.com FPGA projects, Verilog projects, VHDL projects // Image processor unit image_processor image_processor_inst ( .image_pixel_addr(image_pixel_addr1), .image_pixel_val(image_pixel_val1), .clk(clk), .rst(rst), .ccl_start(start), .ccl_th_low(ccl_th_low), .ccl_th_high(ccl_th_high), .ccl_done(ccl_done), .ccl_mem_result_addr(ObjAddr1), .ccl_mem_result_data(ObjInfo) ); // fpga4student.com FPGA projects, Verilog projects, VHDL projects // Create object module CreateObj CreateObjInst ( .clk(clk), .rst(rst), .start(ccl_done), .thresh(ccl_th_low), .ObjInfo(ObjInfo), .ImgVal(ImgVal), .ObjAddr1(ObjAddr1), .ImgAddr(ImgAddr), .Char(ReadCh), .CharCheck(CharCheck), .active(active), .done(done) ); endmodule

Matlab Recognition Results:

Video Demo for the License Plate Recognition System on FPGA:

What is FPGA Programming? FPGA vs Software programming

Recommended and affordable Xilinx FPGA boards for students

Recommended and affordable Altera FPGA boards for students

Recommended Verilog projects:

Recommended and affordable Xilinx FPGA boards for students

Recommended and affordable Altera FPGA boards for students

Recommended Verilog projects:

2. Verilog code for FIFO memory

3. Verilog code for 16-bit single-cycle MIPS processor

4. Programmable Digital Delay Timer in Verilog HDL

5. Verilog code for basic logic components in digital circuits

6. Verilog code for 32-bit Unsigned Divider

7. Verilog code for Fixed-Point Matrix Multiplication

8. Plate License Recognition in Verilog HDL

9. Verilog code for Carry-Look-Ahead Multiplier

10. Verilog code for a Microcontroller

11. Verilog code for 4x4 Multiplier

12. Verilog code for Car Parking System

13. Image processing on FPGA using Verilog HDL

14. How to load a text file into FPGA using Verilog HDL

15. Verilog code for Traffic Light Controller

16. Verilog code for Alarm Clock on FPGA

17. Verilog code for comparator design

18. Verilog code for D Flip Flop

19. Verilog code for Full Adder

20. Verilog code for counter with testbench

21. Verilog code for 16-bit RISC Processor

22. Verilog code for button debouncing on FPGA

23. How to write Verilog Testbench for bidirectional/ inout ports

3. Verilog code for 16-bit single-cycle MIPS processor

4. Programmable Digital Delay Timer in Verilog HDL

5. Verilog code for basic logic components in digital circuits

6. Verilog code for 32-bit Unsigned Divider

7. Verilog code for Fixed-Point Matrix Multiplication

8. Plate License Recognition in Verilog HDL

9. Verilog code for Carry-Look-Ahead Multiplier

10. Verilog code for a Microcontroller

11. Verilog code for 4x4 Multiplier

12. Verilog code for Car Parking System

13. Image processing on FPGA using Verilog HDL

14. How to load a text file into FPGA using Verilog HDL

15. Verilog code for Traffic Light Controller

16. Verilog code for Alarm Clock on FPGA

17. Verilog code for comparator design

18. Verilog code for D Flip Flop

19. Verilog code for Full Adder

20. Verilog code for counter with testbench

21. Verilog code for 16-bit RISC Processor

22. Verilog code for button debouncing on FPGA

23. How to write Verilog Testbench for bidirectional/ inout ports

24. Tic Tac Toe Game in Verilog and LogiSim

25. 32-bit 5-stage Pipelined MIPS Processor in Verilog (Part-1)

26. 32-bit 5-stage Pipelined MIPS Processor in Verilog (Part-2)

27. 32-bit 5-stage Pipelined MIPS Processor in Verilog (Part-3)

28. Verilog code for Decoder25. 32-bit 5-stage Pipelined MIPS Processor in Verilog (Part-1)

26. 32-bit 5-stage Pipelined MIPS Processor in Verilog (Part-2)

27. 32-bit 5-stage Pipelined MIPS Processor in Verilog (Part-3)

29. Verilog code for Multiplexers

30. N bit Adder Design in Verilog

31. Verilog vs VHDL: Explain by Examples

32. Verilog code for Clock divider on FPGA

33. How to generate a clock enable signal in Verilog

34. Verilog code for PWM Generator

35. Verilog coding vs Software Programming

Hello,

ReplyDeleteI am interested in replicating this FPGA project and was wondering if you can provide some code and documentation that I can use. Thank you for your time it is very much appreciated.

thanks,

Roger C.

Please contact me through my email: loi09dt1@gmail.com

DeleteI am doing this same project for final year.Can u plz provide me the code and steps for implementing it.

DeleteThank you in advance

Kindly email me via admin@fpga4student.com

DeleteDo we need any separate program for character recognition and Detection?

ReplyDeleteWe need many more others code for recognition. Not only the code above.

ReplyDeleteDo you have all the codes to implement this on fpga?If yes,can you tell me how to get it?

ReplyDeletedoes anyone have the complete code for this project? will the above code work for the number plate recognition project?

ReplyDeletePlease send me that code, this code is not complete

ReplyDeleteHi, this is just an example code for reference. Full code for this project is not provided.

DeleteI request to all members please provide a full code of this project and tell where I get this full code because I need this code for my final project

DeleteThis project is complicated and it takes time to do. Try to spend some time on it to learn even more.

Delete